## New Release

### LTEC Corporation

Your most experienced partner in IP protection

SiC MOSFET(1200V): ON Semiconductor(equipped in Kia EV6 GT)

Power card Structure, Process analysis Reports.

**Kia EV6 GT (From web information)**

(https://www.kia.com/uk/new-cars/ev6-gt/#text\_441302445)

Power card ap

SiC MOSFET die

#### Report summary

The Kia EV6 GT was announced by Kia Motors, a subordinate of Hyundai Motors, in March 2021, and is high-performance model of the company's first BEV (battery electric vehicle) Kia.

The inverter that drives the rear motor of EV6(2022model) consists of two units. One inverter is for normal mode using Infineon Si-IGBT module, another inverter is added during high output mode using ON Semiconductor (OnSemi) SiC power cards.

This time, LTEC released two reports (1. Structure analysis report and 2. Process analysis report) of OnSemi SiC MOSFET power card equipped in this inverter.

### **Product specifications/features**

Product number: NVVR26A120M1WSS 1200V SiC MOSFET Power card

Product release date: 2022

### **Analysis Contents/Overview of Results**

- 1. Structure analysis Report (98 pages)

- A two-layer metal process is used to maximize transistor area.

- Cu ribbon is used for the source wire, and Ag sinter is used for die attach.

- The power module uses a DBC substrate, and the insulation layer is Al, N based.

- 2. Process analysis Report (42 pages)

- The on-resistance per unit area (RONxA 465m $\Omega$ •mm²) is equivalent to other companies' 2<sup>nd</sup> to 3<sup>rd</sup> generation SiC process.

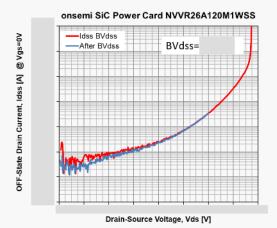

- The thickness of the N-epi (drift) layer and doping concentration are extracted and correlated with the measured breakdown voltage BVdss.

- Estimating the manufacturing process flow and the number of photo/masking steps.

Please contact us for report pricing.

LTEC Corporation US Representative Office www.ltec-biz.com/en/ 2310 Homestead Rd, C1 #231 Los Altos, CA 94024 Phone: +1-(650) 382-1181 contact2@ltec.biz

Report No : 23G-0469-1,2 Release day: 2023.10.31

## (1) Excerpt from structure analysis report

| Content                                                               | Page   |

|-----------------------------------------------------------------------|--------|

|                                                                       |        |

| 1. Device Summary                                                     | <br>3  |

| 1-1. Summary of analysis results                                      | <br>4  |

|                                                                       |        |

| 2. Module analysis                                                    |        |

| 2-1. Product appearance                                               | <br>9  |

| 2-2. Internal layout observation                                      | <br>13 |

| 2-3. The mounted die                                                  | <br>17 |

| 2-4. Module cross-sectional observation                               | <br>18 |

|                                                                       |        |

| 3. SiC MOSFET Structure analysis                                      |        |

| 3-1. Plane structure analysis by Optical Microscope                   | <br>43 |

| 3-2. Plane structure analysis by SEM                                  | <br>59 |

| 3-3. Cell array cross-sectional structure analysis                    | <br>71 |

| 3-4. Cross-sectional structure analysis of MOSFET die outer periphery | <br>77 |

| 3-5. Gate pad cross-sectional structure analysis                      | <br>86 |

| 3-6. Gate wiring cross-sectional structure analysis                   | <br>90 |

|                                                                       |        |

| 4. TEM structure analysis                                             |        |

| 4-1. TEM analysis                                                     | <br>94 |

## (1) Excerpt from structure analysis report

| Number | Measurement points |                  | Measurement        | Material  |

|--------|--------------------|------------------|--------------------|-----------|

| 1      | Mold resin         |                  | -                  | S100 MgGe |

| 2      | Output terminal    |                  |                    | -         |

| 2-1    |                    | Plating layer    | 41.6m              | Sn        |

| 2-2    |                    | Terminal         | 800srm             | Ou        |

| 3      | Solder             |                  | 18 km              | SinAstCor |

| 4      | Cu ribbon          |                  | DODL H             | Cu        |

| 5      | Solder             |                  | 28.6(10)           | Sn/kgCis  |

| 6      | SiC-MOSFET         |                  | -                  | -         |

| 6-1    |                    | Protective film  | <b>电压一个4.00</b> mm | 0.0F      |

| 6-2    |                    | Top electrode 3  | #10mm/200mm        | MAY / TI  |

| 6-3    |                    | Top electrode 2  | 32Am               | AllSLCu)  |

| 6-4    |                    | Top electrode 1  | 15am               | ABSI,DuJ  |

| 6-5    |                    | Substrate        | 730 M H            | 300       |

| 6-6    |                    | Back electrode-1 | 250==              | Ti        |

| 6-7    | Back electrode-2   |                  | 290mm              | MV        |

| 7      | Die attach         |                  | 28 K H             | M         |

| 8      | DBC substrate      |                  | 265 M m            | -         |

| 8-1    |                    | Upper electrode  | 29C H H            | Qu        |

| 8-2    |                    | Insulation layer | 205 M H            | ALMEY.CO  |

| 8-3    |                    | Bottom electrode | 294 (/ H           | Cu        |

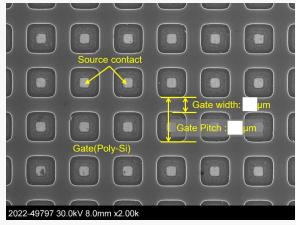

Plane cell array (Poly-Si layer)

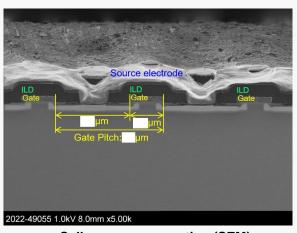

**Cell array cross-section (SEM)**

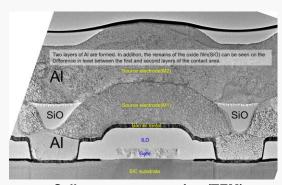

Cell array cross-section (TEM)

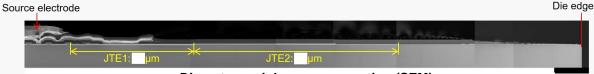

Die outer periphery cross-section (SEM)

# (2) Excerpt from process analysis report

| Co | ntent |                                                                                                                        | Page  |

|----|-------|------------------------------------------------------------------------------------------------------------------------|-------|

| 1  |       | onsemi (equipped in KIA EV6 GT) power card SiC MOSFET: Summary of analysis results······                               | 3     |

|    | 1-1   | Characteristics comparison between onsemi and other companies' SiC MOSFETs                                             | 4     |

|    | 1-2   | SiC MOSFET whole die                                                                                                   | 5     |

|    | 1-3   | Die edge ····                                                                                                          | 6     |

|    | 1-4   | Device structure: SiC MOSFET                                                                                           | 7     |

|    |       | Transistor schematic cross-sectional view ·····                                                                        | 7     |

| 2  |       | SiC MOSFET observation                                                                                                 | 8     |

|    | 2-1   | Cross-sectional and planar structure analysis by SEM                                                                   | 8-16  |

|    |       | Feature of transistor structure and process(1)—(9) ·····                                                               | 8-16  |

|    | 2-2   | Details of self-alignment formation process of N+ and P well                                                           | 17    |

|    |       | Diffusion to define the channel length Lch (estimate) ······                                                           |       |

| 3  |       | onsemi SiC MOSFET NTH4L028N170M1 analysis results summary                                                              | 18    |

|    |       | Table 3-1 Device structure : SiC MOSFET ······                                                                         | 18    |

|    |       | Table 3-2 SiC MOSFET structure : Layers material/thickness                                                             | 19    |

| 4  |       | Manufacturing Process Flow·····                                                                                        | 20    |

|    | 4-1   | SiC MOSFET front-end wafer process flow (estimated) ·······                                                            | 20    |

|    | 4-2   | Cross-sectional schematic views of SiC MOSFET process sequence                                                         | 21-25 |

| 5  |       | Electrical characteristics evaluation                                                                                  | 26    |

|    | 5-1   | onsemi 1200V SiC MOSFET NVVR26A120M1 Id-Vds characteristics                                                            | 27    |

|    | 5-2   | Off-state drain current vs. drain voltage (Vds) and activation energy(Ea) with device Temperature as a parameter······ | 28    |

|    | 5-3   | Off-state breakdown voltage BVdss characteristics                                                                      | 29    |

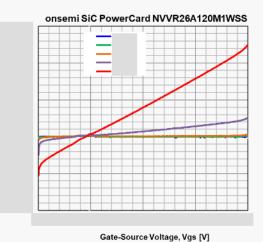

|    | 5-4   | Gate leakage current lgss characteristics                                                                              | 30    |

|    | 5-5.  | Comparison of leakage current between manufactures······                                                               | 31    |

|    | 5-6   | Body diode characteristic                                                                                              | 32    |

|    | 5-7   | Capacitances(Ciss, Coss, Crss)-Vds characteristics ······                                                              | 33    |

|    | 5-8   | Device structure and electrical properties analysis: ON resistance                                                     | 34-36 |

|    | 5-9   | N-epi layer impurity concentration analysis                                                                            | 37    |

|    | 5-10  | Device structure and electrical properties analysis:Breakdown voltage                                                  | 38    |

| 6  |       | Related references                                                                                                     | 39    |

| 7  |       | Related references                                                                                                     | 39-42 |

## (2) Excerpt from process analysis report

Characteristics comparison between onsemi and other companies' SiC MOSFETs

| Maker     | Part no.        | Process<br>generation | Manufacture | Die siz      | ze<br>mm2 | Vdss<br>[V] | RON<br>[mΩ] | Intrinsic<br>RONxA<br>[mΩ•mm²] |

|-----------|-----------------|-----------------------|-------------|--------------|-----------|-------------|-------------|--------------------------------|

| ROHM      | SCT3080KL       | 3rd                   | 2016        | -1.10        |           | 1200        | 80          | 810                            |

| ROHM      | SCT4062KR       | 4th                   | 2022        | 100 1100     | 9.1       | 1200        | 62          | 27%                            |

| WOLFSPEED | C3M0075120K     | 3rd                   | 2017        | 2000 V 0 700 | 10.1      | 1200        | 75          | 1.01                           |

| INFINEON  | AIMW120R060M1H  | 1st+                  | 2021        | 2071 + \$407 | 63        | 1200        | 60          | 201                            |

| Microsemi | MSC040SMA120B   | 2nd                   | 2018        | 100 + 100    | No.       | 1200        | 40          | 100                            |

| GeneSiC   | G3R75MT12K      | 3rd                   | 2020        | 2004 x 8.704 | 40.0      | 1200        | 75          | 234                            |

| onsemi    | NVHL080N120SC1  | 1st SC1               | 2019        | 100 - 100    | 97        | 1200        | 80          | -                              |

| onsemi    | NVVR26A120M1WSS | M1                    | 2023        | 505-01       | 807       | 1200        | 15.6        |                                |

| onsemi    | NTH4L022N120M3S | M3S                   | 2022        | 10.10        | 100       | 1200        | 22          | -                              |

Gate Leakage Current, Igss [A] @ Vds=0V

Off-state breakdown voltage BVdss

Gate leakage current vs. Gate voltage