## Si MOSFET(150V) : iIDEAL Semiconductor SuperQ MOSFET (Super Junction) iS15M7R1S1C Structure Analysis Report

Package

Si MOSFET die

### Report Overview

iIDEAL Semiconductor, a fabless semiconductor manufacturer based in Lehigh Valley, Pennsylvania, has begun mass production of a family of products called SuperQ Power MOSFETs. This SuperQ Power MOSFET technology is derived from an SJ-MOS-like resurf structure, and uses proprietary trench isolation technology and doping concentrations to rival wide bandgap semiconductors in key performance areas such as RonAA and blocking voltage.

This time, LTEC released a structure analysis report that clarifies structure features of this product through plane and cross-section analysis.

### Product Features

**Product type : iS15M7R1S1C  $V_{DS}=150V$ 、 $I_D=133A$ 、 $R_{DS(ON)}=5.4m\Omega$**

**Released data: June 2025**

[Datasheet : <https://idealsemi.com/wp-content/datasheets/iS15M7R1S1C-Datasheet.pdf>](https://idealsemi.com/wp-content/datasheets/iS15M7R1S1C-Datasheet.pdf)

- **Applications:** AI data centers, high voltage DC power conversion, etc.

### Analysis result summary

#### Structure Analysis Report (75 pages)

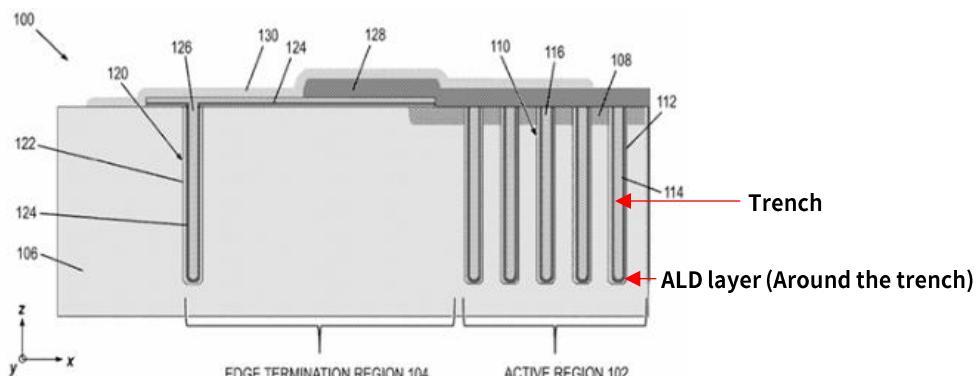

The transistor cells of this product are Si SJ MOSFETs with a trench gate structure, with an ALD (Atomic Layer Deposition) layer formed on the sidewalls of the trench. In terms of performance, when compared to the Infineon 150V SiMOSFET (OptiMOS 5) with a similar rating to this product, the RonxAA of this product is about 2/3 of that of OptiMOS 5.

(\*) A separate SCM analysis is required to confirm the ALD layer. Please contact us for more details. We can also create manufacturing process sequence and electrical characteristic analysis reports for this product. If you are interested, please contact us.

### Report price

Delivery within 1 week after ordering. Please contact us for prices.

| <b>[Table of Contents]</b> |                                                                       | <b>Page</b> |

|----------------------------|-----------------------------------------------------------------------|-------------|

| <b>1</b>                   | <b>Device summary</b>                                                 |             |

|                            | <b>Table1-1: Device summary</b>                                       | • • • 3     |

| <b>1-1.</b>                | <b>Summary of analysis results</b>                                    | • • • 4     |

|                            | <b>Table1-2: Device structure: Si MOSFET</b>                          | • • • 5     |

|                            | <b>Table1-3: Device structure: Layer materials and thickness</b>      | • • • 6     |

|                            | <b>Table1-4: Device structure: Package structure summary</b>          | • • • 7     |

| <b>2</b>                   | <b>Package analysis</b>                                               |             |

|                            | <b>2-1. Appearance observation</b>                                    | • • • 9     |

|                            | <b>2-2. Internal layout observation</b>                               | • • • 11    |

|                            | <b>2-3. Package cross-sectional structure analysis</b>                | • • • 12    |

| <b>3</b>                   | <b>Si MOSFET die structure analysis</b>                               |             |

|                            | <b>3-1. Plane structure analysis by Optical Microscope</b>            | • • • 28    |

|                            | <b>3-2. Plane structure analysis by SEM</b>                           | • • • 42    |

|                            | <b>3-3. Cell array cross-sectional structure analysis</b>             | • • • 51    |

|                            | <b>3-4. Cross-sectional structure analysis of die outer periphery</b> | • • • 64    |

| <b>4</b>                   | <b>Comparison with Infineon's 150V Si MOSFET (OptiMOS 5)</b>          | • • • 72    |

| <b>5</b>                   | <b>(※)Related patent introduction</b>                                 | • • • 74    |

(※)Related patent: US20240145532A1

## Excerpt from Structure Analysis Report

|                                              |                                   |                                                                                     |

|----------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------|

| T <sub>c</sub> = 25°C                        | Infineon OptiMOS 5<br>IPB060N15N5 | iDEAL Semi SuperQ<br>iS15M7R1S1C                                                    |

| V <sub>dss</sub> (V)                         | 150                               | 150                                                                                 |

| Transistor active area AA (mm <sup>2</sup> ) |                                   |                                                                                     |

| R <sub>on</sub> (mΩ / V <sub>gs</sub> (V))   |                                   |                                                                                     |

| R <sub>on</sub> x AA (mΩ · mm <sup>2</sup> ) | 90                                | 60                                                                                  |

| Cell pitch P (μm)                            |                                   |                                                                                     |

| Cell structure features                      |                                   | Gate (Poly-Si) trench, ALD trench<br>(ALD layer doping (P type) on trench sidewall) |

### Comparison with Infineon's 150V Si MOSFET (OptiMOS 5)

#### (19) United States

(12) Patent Application Publication (10) Pub. No.: US 2024/0145532 A1

Jauregui et al. (43) Pub. Date: May 2, 2024

(54) COMBINED CHARGE BALANCE AND EDGE TERMINATION SURFACE PASSIVATION FOR A SEMICONDUCTOR DEVICE AND METHODS OF FABRICATING THE SAME

(52) U.S. CL.

CPC ..... H01L 29/0615 (2013.01); H01L 21/71 (2013.01); H01L 23/62 (2013.01)

(71) Applicant: IDEAL SEMICONDUCTOR DEVICES, INC., Bethlehem, PA (US)

(57) ABSTRACT

(72) Inventors: David Jauregui, Bethlehem, PA (US); Stanislav Solov'yev, Breinigsville, PA (US); Philip Rutter, Bethlehem, PA (US)

A semiconductor device is provided that includes an epitaxial layer disposed on a semiconductor substrate, the epitaxial layer including an active region, in which at least one active element is formed, and an edge termination region, in which at least one edge termination structure is formed, the edge termination region being laterally adjacent to the active region. The semiconductor device further includes a charged layer disposed on an upper surface of the epitaxial layer, the charged layer covering at least a portion of the active region and extending laterally over at least a portion of the edge termination region. Active trenches may be formed in the active region, and at least one edge trench may be formed in the edge termination region. The charged layer may be formed on sidewalls of each of the active trenches and the edge trench using atomic layer deposition in a same processing step.

(21) Appl. No.: 18/464,686

(22) Filed: Sep. 11, 2023

Related U.S. Application Data

(60) Provisional application No. 63/420,339, filed on Oct. 28, 2022.

Publication Classification

(51) Int. Cl.

H01L 29/06 (2006.01)

H01L 21/71 (2006.01)

H01L 23/62 (2006.01)

### Related Patent Overview (US20240145532A1)

### Related patent drawings (US20240145532A1)